## Solution four Q.P. code: 13320 Subject : Digital Electronics CMTRX)

8) a) Shift Reg :>

The binary data in vegister can be moved within the ozeg. from one FF to another. The oreg. that allows such data toransfer.

"us called as shift Req Data can be entered in Serial our parallel fourn & can be oretorieved in serial &

There are four possible moder of o peration.

(B SISO @ SIPO 3 PISO @ PIPO Application of shift Reg. sequence generations.

b) Durawback of Synch. Counter.

clock Skew

- It is a phenomenon in Synchronous digital · Systems in which the same sourced clock signal arrives at diff. Component out different times : ie instanteneous diff. been the ureading of any two clocks us called their clock skew.

| 0) | Half Adder                              |    |

|----|-----------------------------------------|----|

|    | A · · · · · · · · · · · · · · · · · · · | -S |

| TIP |       | TOIP |       |

|-----|-------|------|-------|

| B   | S     | C    |       |

| 0   | .0    | 0    |       |

| 1   | 1     | 0    |       |

| 10  | 117   | 0'   | 1     |

| 1   | 0     | 1    | 1     |

|     | B 0 1 | B S  | B S C |

Scanned by CamScanner

Scanned by CamScanner

Scanned by CamScanner

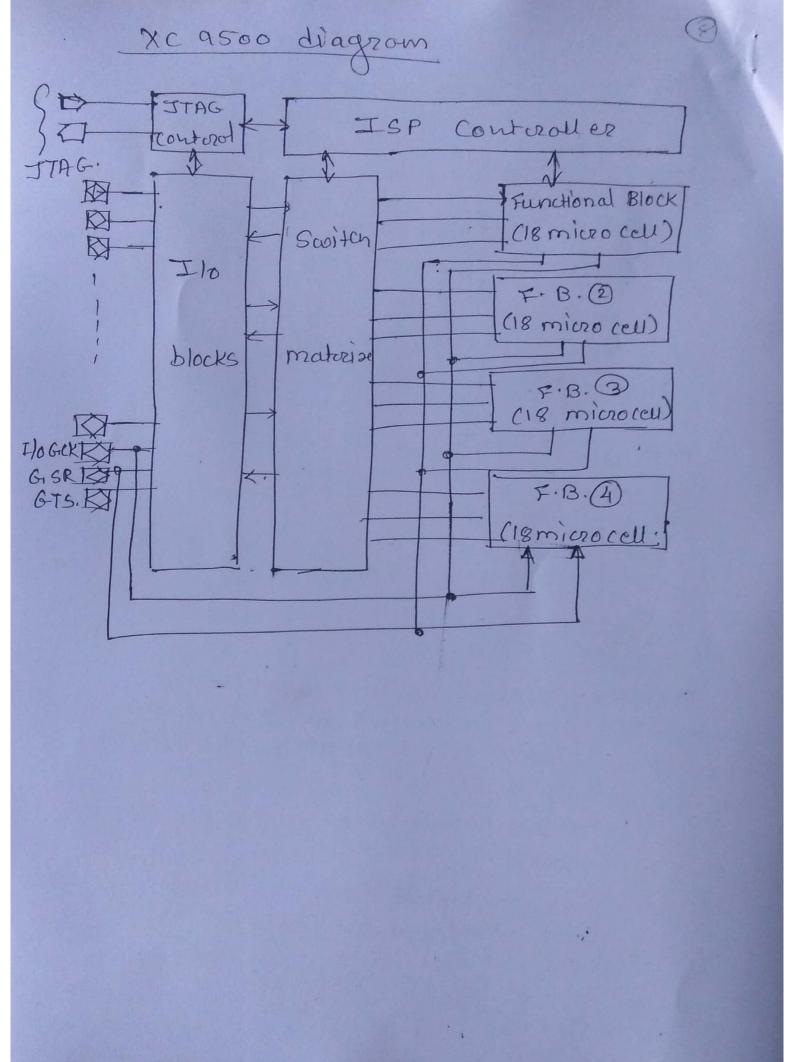

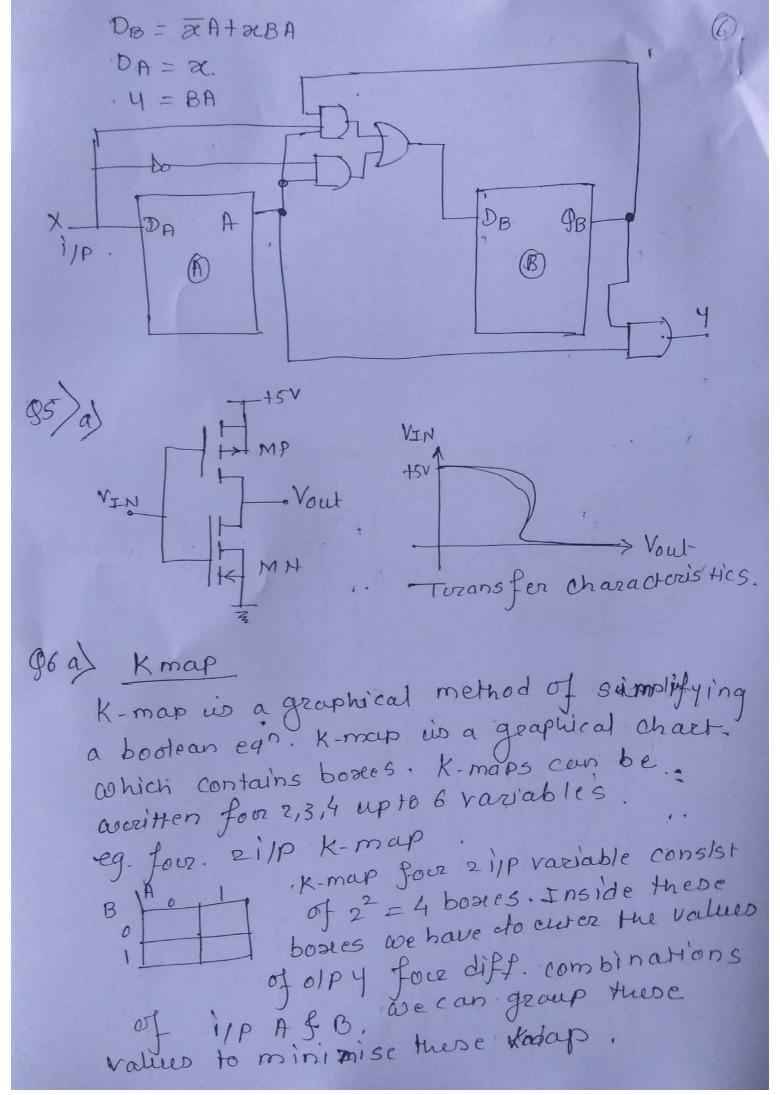

Mealy & Moove seg. Machine There are too sequential logic design models. Mealy Model Externa XN.S. Monorey > 0/p. > Logic Elements ·N·S.'= 01P = f(P.S., i1P's) Moore Model N.s. = f (P.s. & 1/Ps) OIP = f. (P.S.) XC9500 family XC9500 CPLD is xilinx architecture. Internal PLD's in XilinX are called as functional blocks. Each PLD has 36 ilp's of 18 microcells & olp's -1+ ere Ilo pins can be used as ilp, olp. our bidiorectional ilp Here, GCK -> Global clock GISR -> Orlobal Set/Reach GTS -> Global three State Conterd. En diag ture are four FB's. Instead we can up to up to 16 FB's, centiere each FB cuill receive 36 signals from switch material.